# R65C52 DUAL ASYNCHRONOUS COMMUNICATIONS INTERFACE ADAPTER (DACIA)

#### PRELIMINARY

#### **DESCRIPTION**

The Rockwell CMOS R65C52 Dual Asynchronous Communications Interface Adapter (DACIA) provides an easily implemented, program controlled interface between 8-bit microprocessor-based systems and serial communication data sets and modems.

The DACIA has an internal baud rate generator. This feature eliminates the need for multiple component support circuits, a crystal being the only other part required. The Transmitter baud rate can be selected under program control to be either 1 of 15 different rates from 50 to 38,400 baud, or at 1/16 times an external clock rate. The Receiver baud rate may be selected under program control to be either the Transmitter rate, or at 1/16 times the external clock rate. The DACIA is programmable for word lengths of 5, 6, 7 or 8 bits; even, odd, or no parity; and 1 or 2 stop bits.

The DACIA is designed for maximum programmed control from the microprocessor (MPU) to simplify hardware implementation. Dual sets of registers allow independent control and monitoring of each channel. The DACIA also provides a unique, programmable Automatic Address Recognition Mode for use in a multidrop environment.

The Control Register and Status Register permit the MPU to easily select the R65C52's operating modes and determine operational status.

The Interrupt Enable Registers (IER) and Interrupt Status Registers (ISR) allow the MPU to control and monitor the interrupt capabilities of the DACIA.

The Control and Format Register (CFR) permits selection of baud rates, word lengths, parity and stop bits as well as control of DTR and RTS output signals.

The Status Register (SR) gives the MPU access to the state of the modem control lines, framing error, transmitter underrun and break conditions.

The Compare Data Registers (CDR) hold the data value to be used in the compare mode and the Transmit Break Register (TBR) commands a Transmit Break and provides for parity/address recognition, for Automatic Address Mode.

The Transmitter Data Register and Receiver Data Register are used for temporary data storage of input and output data.

#### **FEATURES**

- · Low power CMOS N-well silicon gate technology

- Two independent full duplex channels with buffered receivers and transmitters.

- Data set/modem control functions

- Internal baud rate generator with 15 programmable baud rates (50 to 38,400)

- Program-selectable internally or externally controlled receiver rate

- Programmable word lengths, number of stop bits, and parity bit generation and detection

- · Programmable interrupt control

- Programmable control of edge detect for DCD, DSR, DTR, RTS, and CTS

- · Program-selectable serial echo mode for each channel

- Automatic Address Recognition Mode for multi-drop operation.

- . Up to 4 MHz host bus operation

- 5.0 Vdc ±5% supply requirements

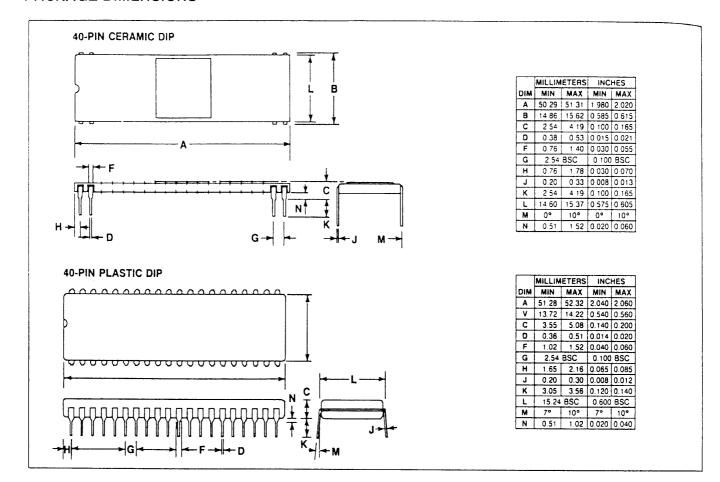

- · 40-pin plastic or ceramic DIP

- Full TTL or CMOS input/output compatibility

- Compatible with R6500 and R65C00 microprocessors and R6500/\* microcomputers.

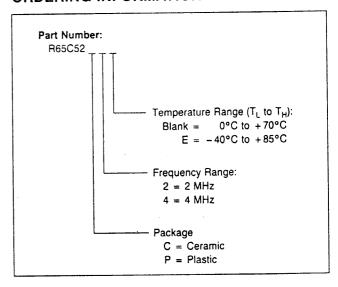

#### ORDERING INFORMATION

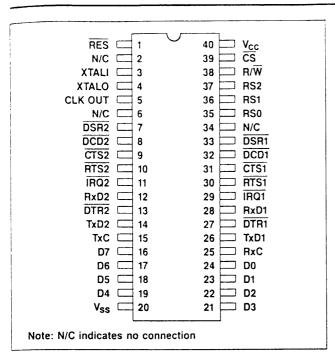

Figure 1. R65C52 Pin Configuration

#### INTERFACE SIGNALS

Figure 2 shows the DACIA interface signals associated with the microprocessor and the modem.

#### DATA BUS (D0-D7)

The D0–D7 pins are eight data lines that transfer data between the microprocessor (MPU) and the DACIA. These lines are bidirectional and are normally high-impedance except during READ cycle when the DACIA is selected.

#### REGISTER SELECTS (RS0, RS1, RS2)

The three register select lines are normally connected to the processor address lines to allow the MPU to select the various internal registers. Table 1 shows the internal register select coding and identifies the abbreviations (ABBR) used throughout the text for each register.

#### READ/WRITE (R/W)

The  $R/\overline{W}$  input, generated by the microprocessor, controls the direction of data transfer. A high on the  $R/\overline{W}$  line indicates a read cycle, while a low indicates a write cycle.

#### CHIP SELECT (CS)

The chip select input is normally connected to the processor address lines either directly or through decoders. The DACIA latches address and  $R/\overline{W}$  inputs on the falling edge of  $\overline{CS}$  and latches the data bus inputs on the rising edge of  $\overline{CS}$ .

#### RESET (RES)

During system initialization a low level on the RES input causes a RESET to occur. At this time the IER's are set to \$80, the DTR and RTS lines go to the high state, the RDR register is cleared, the TBR is set to \$0F, the compare mode is disabled, and the CTS, DCD, DSR flags are cleared. No other bits are affected.

#### TRANSMIT DATA (TXD1, TXD2)

The TxD outputs transfer serial non-return to zero (NRZ) data to the data communications equipment (DCE). The data is transferred, LSB first, at a rate determined by the baud rate generator.

#### **RECEIVE DATA (RXD1, RXD2)**

The RxD inputs transfer serial NRZ data into the DACIA from the DCE, LSB first. The receiver baud rate is determined by the baud rate generator.

Figure 2. DACIA Interface Signals

#### CLEAR TO SEND (CTS1, CTS2)

The  $\overline{\text{CTS}}$  control line inputs allow handshaking by the transmitter. When  $\overline{\text{CTS}}$  is low, the data is transmitted continuously. When  $\overline{\text{CTS}}$  is high, the Transmit Data Register empty bit in the ISR is not set. The word presently in the Transmit Shift Register is sent normally. Any active transition on the  $\overline{\text{CTS}}$  lines sets the  $\overline{\text{CTS}}$  bit in the appropriate ISR. The  $\overline{\text{CTS}}$  status bit in the CSR reflects the current high or low state of  $\overline{\text{CTS}}$ .

# DATA CARRIER DETECT (DCD1, DCD2)

These two lines may be used as general purpose inputs. An active transition sets the  $\overline{DCD}$  bit in the ISR. The  $\overline{DCD}$  bit in the CSR reflects the current state of the  $\overline{DCD}$  line.

## DATA SET READY (DSR1, DSR2)

These two lines may be used as general purpose inputs. An active transition sets the  $\overline{\rm DSR}$  bit in the ISR. The  $\overline{\rm DSR}$  bit in the CSR reflects the current state of the  $\overline{\rm DSR}$  line.

#### REQUEST TO SEND (RTS1, RTS2)

These two lines may be used as general purpose outputs. They are set high upon reset. Their state may be programmed by setting the appropriate bits in the CFR high or low. The state of the  $\overline{\text{RTS}}$  line is reflected by the  $\overline{\text{RTS}}$  bit in the CSR.

# DATA TERMINAL READY (DTR1, DTR2)

These two lines may be used as general purpose outputs. They are set high upon reset. Their state may be programmed by setting the appropriate bits in the CFR high or low. The state of the  $\overline{\text{DTR}}$  line is reflected by the  $\overline{\text{DTR}}$  bit in the CSR.

# INTERRUPT REQUEST (IRQ1, IRQ2)

The  $\overline{\text{IRQ}}$  lines are open-drain outputs from the interrupt control logic.  $\overline{\text{IRQ1}}$  is associated with ACIA1 and  $\overline{\text{IRQ2}}$  is associated with ACIA2. These lines are normally high but go low when one of the flags in the ISR is set, provided that its corresponding enable bit is set in the IER.

Table 1. DACIA Register Selection

|             | REG | ISTER SELI<br>LINES | ECT  | CONTROL AN |          | REG          | REGISTER ACCESS                |                                |

|-------------|-----|---------------------|------|------------|----------|--------------|--------------------------------|--------------------------------|

| HEX<br>ADDR | RS2 | RS1                 | RS0  | CFR-7      | CFR-6    | ABBR         | WRITE                          | READ                           |

| 00          | L   | L                   | L    |            | -        | IER1<br>ISR1 | INTERRUPT ENABLE<br>REGISTER 1 | INTERRUPT STATUS<br>REGISTER 1 |

|             |     |                     |      | 0          | -        | CFR1<br>SR1  | CONTROL<br>REGISTER 1          | STATUS<br>REGISTER 1           |

| 01          | L   | L                   | н    | 1          | _        | CFR1         | FORMAT<br>REGISTER 1           | INVALID                        |

|             |     |                     |      |            | 0        | CDR1         | COMPARE DATA<br>REGISTER 1     | INVALID                        |

| 02          | L   | н                   | L    |            | 1        | TBR1         | TRANSMIT BREAK<br>REGISTER 1   | INVALID                        |

| 03          | L   | Н                   | Н    | _          | _        | TDR1<br>RDR1 | TRANSMIT DATA<br>REGISTER 1    | RECEIVE DATA<br>REGISTER 1     |

| 04          | н   | L                   | L    |            | _        | IER2<br>ISR2 | INTERRUPT ENABLE<br>REGISTER 2 | INTERRUPT STATUS<br>REGISTER 2 |

|             |     |                     |      | 0          | <u>-</u> | CFR2<br>SR2  | CONTROL<br>REGISTER 2          | STATUS<br>REGISTER 2           |

| 05          | н   | L                   | Н    | 1          |          | CFR2         | FORMAT<br>REGISTER 2           | INVALID                        |

|             |     |                     |      | _          | . 0      | CDR2         | COMPARE DATA<br>REGISTER 2     | INVALID                        |

| 06          | н,  | Н                   |      | -:         | 1        | TBR2         | TRANSMIT BREAK REGISTER 2      | INVALID                        |

| 07          | Н   | Н                   | C, H |            | _        | TDR2<br>RDR2 | TRANSMIT DATA REGISTER 2       | RECEIVE DATA<br>REGISTER 2     |

#### **FUNCTIONAL DESCRIPTION**

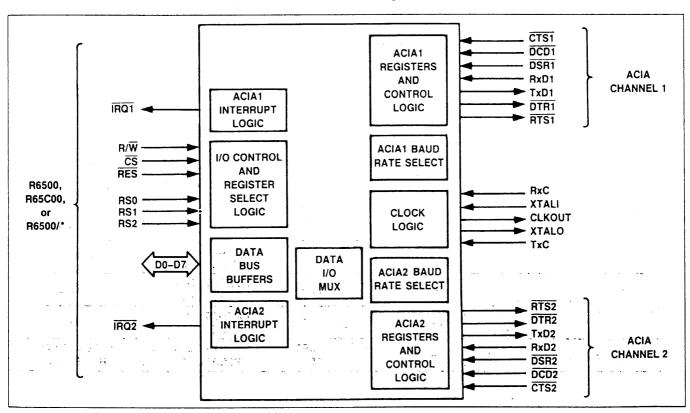

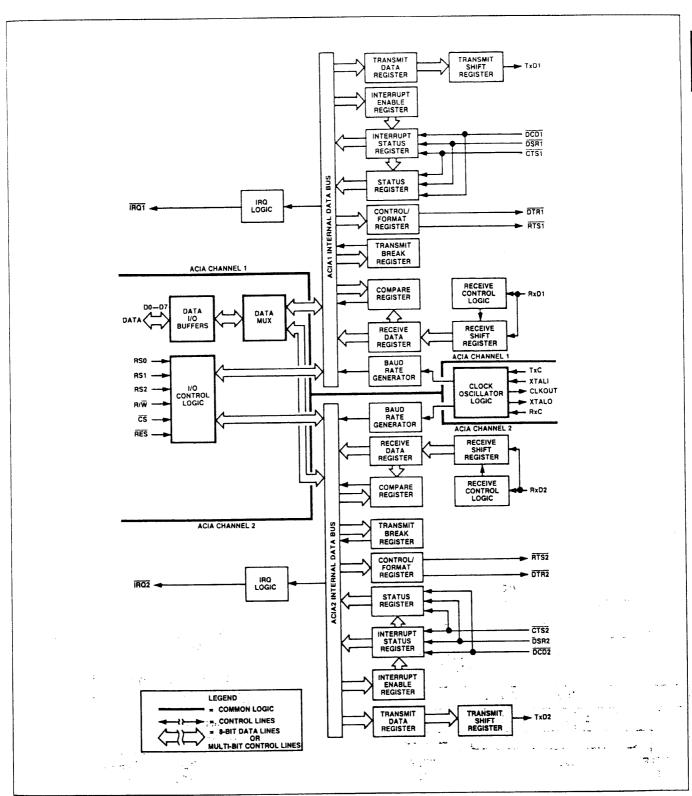

Figure 3 is a block diagram of the DACIA which consists of two asynchronous communications interface adapters with common microprocessor interface control logic and data bus buffers. The individual functional elements of the DACIA are described in the following paragraphs.

#### INTERRUPT LOGIC

The interrupt logic causes the  $\overline{\text{IRQ}}$  lines ( $\overline{\text{IRQ1}}$  or  $\overline{\text{IRQ2}}$ ) to go low when conditions are met that require the attention of the MPU. There are two registers (the Interrupt Enable Register and the Interrupt Status Register) involved in the control of interrupts in the DACIA. Corresponding bits in both registers must be set to cause an  $\overline{\text{IRQ}}$ .

Figure 3. DACIA Block Diagram

#### DATA BUS BUFFER

The Data Bus Buffer is a bidirectional interface between the system data lines and the internal data bus. When  $R/\overline{W}$  is low and  $\overline{CS}$  is low, the Data Bus Buffer writes data from the internal data bus to the system data lines. When  $R/\overline{W}$  is high and  $\overline{CS}$  is low, data is driven into the DACIA from the system data bus. Table 2 summarizes the Data Bus Buffer states.

Table 2. Data Bus Buffer Summary

| Contro<br>R/W | ol Signals<br>CS | Data Bus Buffer State   |

|---------------|------------------|-------------------------|

| L             | L                | Write Mode — Tri-State  |

| Н             | L                | Read Mode — Output Data |

#### TRANSMIT AND RECEIVE DATA REGISTERS

These registers are used as temporary data storage for the DACIA Transmit and Receive circuits. The Transmit Data Register is characterized as follows:

- Bit 0 is the leading bit to be transmitted.

- Unused data bits are the high-order bits and are "don't care" for transmission.

- · Write-only register.

The Receive Data Register is characterized in a similar fashion as follows:

- · Bit 0 is the leading bit received.

- Unused data bits are the high order bits and are "0" for the receiver

- Parity bits are not contained in the Receive Data Register, but are stripped off after being used for external parity checking. Parity and all unused high-order bits are "0".

- · Read-only register

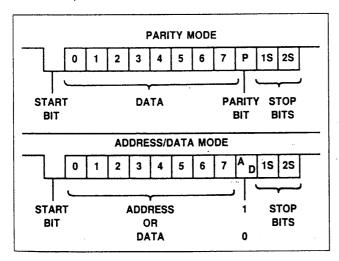

Figure 4 shows an example of a Parity Mode single transmitted or received data word. In this example, the data word is formatted with 8 data bits, parity, and two stop bits. Figure 4 also shows a single character transmitted or received in Address/Data Mode. In this example, the address or data word is 8 bits, there is no

Figure 4. Typical Character

parity bit, and there are two stop bits. The 10th bit (normal parity bit) is an address/data indicator. A 1 means the 8 bits are an address and a 0 means the 8 bits are data.

#### **CLOCK CIRCUIT**

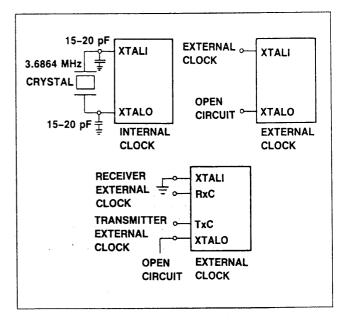

The internal clock oscillator supplies the time base for the baud rate generator. The oscillator can be driven by a crystal or an external clock, or it can be disabled, in which case the time base for the baud rate is generated by the Receiver External Clock (RxC) and Transmitter External Clock (TxC) input pins. Figure 5 shows the three possible clock configurations.

#### Crystal (XTALI, XTALO)

These pins are normally connected to an external 3.6864 MHz crystal used as the time base for the baud rate generator. As an alternative, the XTLI pin may be driven with an externally generated clock in which case the XTALO pin must float.

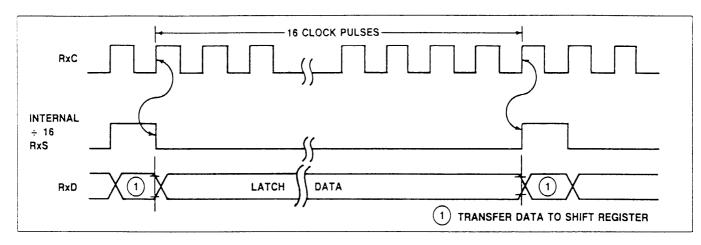

#### Receiver Clock (RxC)

This pin is the Receiver 16x clock input when the baud rate generator is programmed for external clock. Figure 15 shows timing considerations for RxC.

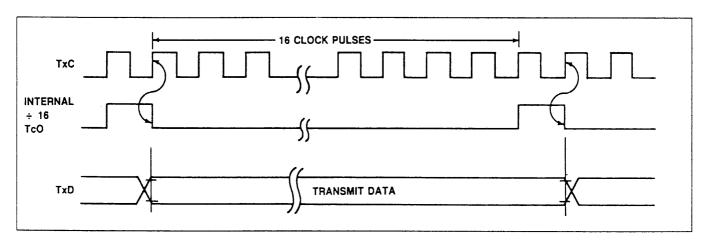

#### Transmitter Clock (TxC)

This pin is the transmitter 16x clock input when the baud rate generator is programmed for external clock. Figure 16 shows timing considerations for TxC.

#### Note

When RxC and TxC are used for external clock input, XTALI must be tied to ground (Vss) and XTALO must be left open (floating).

#### Clock Out (CLK OUT)

This output is a buffered output from the 3.6864 MHz crystal oscillator. It may be used to drive the XTALI input of another DACIA. This allows multiple DACIA chips to be used in a system with only one crystal needed. CLK OUT is in phase with XTALI.

Figure 5. DACIA Clock Generation

# CONTROL AND FORMAT REGISTER (CFR)

The Control and Format Register (CFR) is a dual-function, writeonly register which allows control of word length, baud rate, control line outputs, parity, echo mode, and compare/TBR access. When the CFR is written to with bit 7 = 0, the CFR functions as a Control Register. When the CFR is written to with bit 7 = 1, the CFR operates as a Formal Register.

## Control Register (CFR Addressed with Bit 7 = 0)

| 7 | 6       | 5                   | 4    | 3   | 2      | 1                  | 0    |

|---|---------|---------------------|------|-----|--------|--------------------|------|

| 0 | TBR/CDR | NO.<br>STOP<br>BITS | ECHO | BAU | D RATE | SELEC <sup>*</sup> | TION |

|   | Bit<br>0       | 7   |   | Control or Format Register Control Register                                             |

|---|----------------|-----|---|-----------------------------------------------------------------------------------------|

|   | <b>Bit</b> 1 0 | -   |   | TBR/CDR Access the Transmit Break Register (TBR) Access the Compare Data Register (CDR) |

|   | <b>Bit</b> 1 0 |     |   | Number of Stop Bits Per Character<br>Two stop bits<br>One stop bit                      |

|   | Bit<br>1       |     |   | Echo Selection (ECHO) Echo activated Echo deactivated                                   |

| E | 3its           | 3-0 | ) | Baud Rate Selection                                                                     |

| 3 | 2              | 1   | 0 | Baud Rate                                                                               |

| 0 | 0              | 0   | 0 | 50                                                                                      |

| 0 | 0              | 0   | 1 | 109.2                                                                                   |

| 0 | 0              | 1   | 0 | 134.58                                                                                  |

| 0 | 0              | 1   | 1 | 150                                                                                     |

| 0 | 1              | 0   | 0 | 300                                                                                     |

| 0 | 1              | 0   | 1 | 600                                                                                     |

| 0 | 1              | 1   | 0 | 1200                                                                                    |

| 0 | 1              | 1   | 1 | 1800                                                                                    |

| 1 | 0              | 0   |   | 2400                                                                                    |

| 1 | 0              | -   | 1 | 3600                                                                                    |

| 1 | 0              | 1   |   | 4800                                                                                    |

| 1 | 0              | 1   | 1 | 7200                                                                                    |

| 1 | 1              | 0   | 0 | 9600                                                                                    |

0 1

1 0 19200

38400

External TxC and RxC Clocks

#### Format Register (CFR Addressed with Bit 7 = 1)

| 7 | 6  | 5                  | 4            | 3 | 2                | 1              | 0              |

|---|----|--------------------|--------------|---|------------------|----------------|----------------|

| 1 | OF | IBER<br>DATA<br>TS | PAR<br>SELEC |   | PARITY<br>ENABLE | DTR<br>CONTROL | RTS<br>CONTROL |

| Bit 7                                       | Control or Format Register<br>Format Register                                 |

|---------------------------------------------|-------------------------------------------------------------------------------|

| Bits 6-5<br>6 5<br>0 0<br>0 1<br>1 0<br>1 1 | Number of Data Bits Per Character<br>No. Bits<br>5<br>6<br>7                  |

| Bits 4-3<br>4 3<br>0 0<br>0 1<br>1 0<br>1 1 | Parity Mode Selection Selects Odd Parity Even Parity Mark Parity Space Parity |

| Bit 2<br>1<br>0                             | Parity Enable Parity as specified by bits 4-3 No Parity                       |

| <b>Bit 1</b><br>1<br>0                      | DTR Control DTR high DTR low                                                  |

| <b>Bit 0</b> 1 0                            | RTS Control RTS high RTS low                                                  |

## INTERRUPT ENABLE REGISTER (IER)

The Interrupt Enable Register (IER) is a write-only register that allows each of the possible IRQ sources to be enabled, or disabled, individually without affecting any of the other interrupt enable bits in the register. IRQ sources are enabled by writing to the IER with bit 7 set to a 1 and every bit set to a 1 that corresponds to the IRQ source to be enabled. IRQ sources are disabled by writing to the IER with bit 7 set to a 0 and every bit set to a 1 that corresponds to the IRQ source to be disabled. Any bit (except bit 7) to which a 0 is written is unaffected and remains in its original state. As an example, writing \$7F to the IER will disable all IRQ source bits, but writing \$FF to the IER will enable all IRQ source bits. A hardware reset (RES) clears all IRQ source bits to the 0 state. Bit assignments for the IER are as follows:

| 7                     | 6                  | 5         | 4         | 3         | 2                     | 1                              | 0                 |

|-----------------------|--------------------|-----------|-----------|-----------|-----------------------|--------------------------------|-------------------|

| CLEAR/<br>SET<br>BITS | TDR<br>EMPTY<br>IE | CTS<br>IE | DCD<br>IE | DSR<br>IE | PARITY<br>ERROR<br>IE | FRM<br>OVR<br>BRK<br>CPR<br>IE | RDR<br>FULL<br>IE |

# INTERRUPT STATUS REGISTER (ISR)

The Interrupt Status Register (ISR) is a read-only register that identifies the current status condition for each DACIA internal IRQ source. Bits 6 through 0 of the ISR are set to a 1 whenever the corresponding IRQ source condition has occurred in the DACIA. Bit 7 identifies if any of the IRQ source status bits have been set in the ISR.

| 7                 | 6            | 5            | 4            | 3            | 2               | 1                        | 0           |

|-------------------|--------------|--------------|--------------|--------------|-----------------|--------------------------|-------------|

| ANY<br>BIT<br>SET | TDR<br>EMPTY | CTS<br>TRANS | DCD<br>TRANS | DSR<br>TRANS | PARITY<br>ERROR | FRM<br>OVR<br>BRK<br>CPR | RDR<br>FULL |

| Bit 7<br>1<br>0 | Any Bit Set Any bit (6 through 0) has been set to a 1 No bits have been set to a 1                                                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Bit 6<br>1      | Transmit Data Register Empty (TDR EMPTY) Transmit Data Register has been transferred to the shift register                        |

| 0               | New data has been written to the Transmit Data<br>Register                                                                        |

| Bit 5           | Transition On CTS Line (CTS TRANS)  A positive or negative transition has occurred on CTS                                         |

| 0               | No transition has occurred on CTS, or ISR has been Read                                                                           |

| Bit 4<br>1      | Transition On DCD Line (DCD TRANS)  A positive or negative transition has occurred on DCD                                         |

| 0               | No transition has occurred on DCD, or ISR has been Read                                                                           |

| Bit 3<br>1      | Transition On DSR Line (DSR TRANS)  A positive or negative transition has occurred on DSR                                         |

| 0               | No transition has occurred on DSR, or ISR has been Read                                                                           |

| Bit 2           | Parity Error                                                                                                                      |

| 1<br>0          | A parity error has occurred in received data<br>No parity error has occurred, or the Receive<br>Data Register (RDR) has been Read |

| Bit 1           | Frame Error, Overrun or Break (FRM, OVR, BRK, CPR)                                                                                |

| 1               | A framing error, receive overrun, or receive break has occured, or, in Compare Mode                                               |

| <b>0</b>        | No error, overrun, break has occured, RDR has been Read, or not in Compare Mode                                                   |

| Bit 0<br>1      | Receive Data Register Full (RDR FULL) Shift register data has been transferred to Receive Data Register                           |

| 0               | Receive Data Register has been Read                                                                                               |

# CONTROL STATUS REGISTER (CSR)

The Control Status Register (CSR) is a read-only register that provides I/O status and error condition information. The CSR is normally read after an IRQ has occurred to determine the exact cause of the interrupt condition.

| 7                | 6     | 5             | 4             | 3 | 2 | 1              | 0             |

|------------------|-------|---------------|---------------|---|---|----------------|---------------|

| FRAMING<br>ERROR | TRANS | CTS<br>STATUS | DCD<br>STATUS |   |   | DTA.<br>STATUS | RTS<br>STATUS |

| Bit 7<br>1<br>0 | Framing Error A framing error occurred in receive data No framing error occurred, or the RDR was Read                                   |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6<br>1      | Transmitter Underrun (TRANS UNDR) Transmit shift register is empty and TDRE bits in IER and ISR are set A write to the TDR has occurred |

| Bit 5<br>1<br>0 | CTS Status  A low-to-high transition occurred on CTS line  A high-to-low transition occurred on CTS line                                |

| Bit 4<br>1<br>0 | DCD Status A low-to-high transition occurred on DCD line A high-to-low transition occurred on DCD line                                  |

| Bit 3<br>1<br>0 | DSR Status  A low-to-high transition occurred on DSR line  A high-to-low transition occurred on DSR line                                |

| Bit 2<br>1<br>0 | REC Break A Receive Break has occurred No Receive Break occurred, or RDR, was read                                                      |

| Bit 1<br>1<br>0 | DTR Status A low-to-high transition occurred on DTR line A high-to-low transition occurred on DTR line                                  |

| Bit 0<br>1<br>0 | RTS Status A low-to-high transition occurred on RTS line A high-to-low transition occurred on RTS line                                  |

# Dual Asynchronous Communications Interface Adapter (DACIA)

#### TRANSMIT BREAK REGISTER (TBR)

The DACIA has two Transmit Break Registers which are writeonly registers. Only two bits of these registers are used; one during the Receive mode to command a Transmit Break and the other to provide for Parity/Address recognition. Writing a 1 to bit 1 of the TBR causes a continuous Break to be transmitted by the ACIA associated with the register. Writing a 0 to this bit allows normal transmission to resume. Writing a 1 to bit 0 of the TBR commands the value of the Parity bit to be sent to the Parity Error bit (bit 2 of the ISR). Writing a 0 to this bit allows normal Parity Error recognition to be in force. When an RES is received by the DACIA, both of these bits are reset to 0. The bits format for the TBR are as follows:

| 7 | 6 | 5   | 4    | 3 | 2 | 1            | 0            |

|---|---|-----|------|---|---|--------------|--------------|

|   |   | NOT | JSED |   |   | TRANS<br>BRK | PAR/<br>ADDR |

| Not used (don't care)                          |

|------------------------------------------------|

| Transmit Break (TRANS BRK)                     |

| Transmit continuous Break until disabled       |

| Resume normal transmission                     |

| Parity/Address Recognition (PAR ADDR)          |

| Send value of parity to ISR bit 2              |

| Return to normal Parity Error recognition mode |

|                                                |

#### COMPARE DATA REGISTER

The Compare Data Register (CDR) is a write-only register which can be accessed when CFR bit 6 = 0. By writing a value into the CDR, the DACIA is put in the compare mode. In this mode, setting of the RDRF bit is inhibited and the FRM/OVR/BRK/CPR bit (bit 1) on the ISR is set until a character is received which matches the value in the CDR. The next character is then received and the RDRF bit is set. The receiver will now operate normally until the CDR is again loaded.

#### SUMMARY OF REGISTERS

Table 3 shows the control and status registers associated with the DACIA in a single summary table. Each of the ACIA's has its own set of these seven registers.

#### **OPERATION**

The following paragraphs describe ten modes (or conditions) of operation of the DACIA. The modes described are:

- Continuous Data Transmit

- Continuous Data Receive

- Transmit Underrun Condition

- Effects of CTS on Transmitter

- Effects of Overrun on Receiver

- Echo Mode Timing

- Framing Error

- Transmit Break Character

- Receive Break Character

- Automatic Address Recognition

Table 3. Control and Status Registers Format Summary

| REGISTER BIT NUMBERS |                                                                              |               |               |               |                       |                            |                             | REGISTER                         | RES  |

|----------------------|------------------------------------------------------------------------------|---------------|---------------|---------------|-----------------------|----------------------------|-----------------------------|----------------------------------|------|

| 7                    | 6                                                                            | 5             | 4             | 3             | 2                     | 1                          | 0                           |                                  |      |

| CLEAR/SET<br>BITS    | TDR<br>EMPTY<br>IE                                                           | CTS<br>IE     | DCD<br>IE     | DSR<br>IE     | PARITY<br>ERROR<br>IE | FRM, OVR<br>BRK, CPR<br>IE | RDR<br>FULL<br>IÉ           | INTERRUPT<br>ENABLE<br>REGISTERS | \$80 |

| ANY<br>BIT<br>SET    | TDR<br>EMPTY                                                                 | CTS<br>TRANS  | DCD<br>TRANS  | DSR<br>TRANS  | PARITY<br>ERROR       | FRM, OVR<br>BRK, CPR       | RDR<br>FULL                 | INTERRUPT<br>STATUS<br>REGISTERS | _    |

| FRAMING<br>ERROR     | TRANS<br>UNDR                                                                | CTS<br>STATUS | DCD<br>STATUS | DSR<br>STATUS | REC<br>BREAK          | DTR<br>STATUS              | RTS<br>STATUS               | STATUS<br>REGISTERS              | _    |

| 0                    | 0 TBR/ STOP ECHO BAUD RATE SELECTION BITS                                    |               |               |               |                       |                            | CONTROL<br>REGISTERS<br>AND | _                                |      |

| 1                    | 1 NUMBER OF PARITY PARITY DTR RTS DATA BITS SELECTION ENABLE CONTROL CONTROL |               |               |               |                       |                            |                             | FORMAT<br>REGISTERS              |      |

|                      | NOT USED TRANS PAR/<br>BRK ADDR                                              |               |               |               |                       |                            |                             |                                  | \$0F |

|                      | COMPARE BITS (ADDRESS RECOGNITION)                                           |               |               |               |                       |                            |                             | COMPARE<br>DATA<br>REGISTERS     | _    |

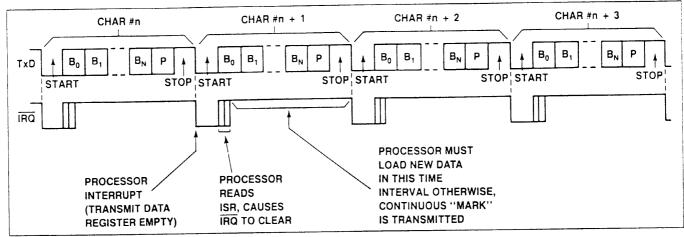

#### CONTINUOUS DATA TRANSMIT

In the normal operating mode, the TDRE bit in the ISR signals the MPU that the DACIA is ready to accept the next data word. An IRQ occurs if the corresponding TDRE IRQ enable bit is set in the IER. The TDRE bit is set at the beginning of the start bit.

When the MPU writes a word to the TDR the TDRE bit is cleared. In order to maintain continuous transmission the TDR must be loaded before the stop bit(s) are ended. Figure 6 shows the relationship between  $\overline{IRQ}$  and TxD for the Continuous Data Transmit mode.

Figure 6. Continuous Data Transmit

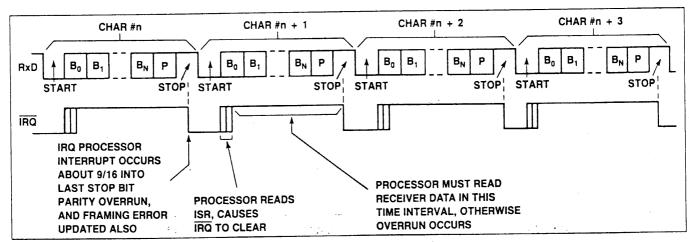

#### **CONTINUOUS DATA RECEIVE**

Similar to the continuous data transmit mode, the normal receive mode sets the RDRF bit in the ISR when the DACIA has received a full data word. This occurs at about the 9/16 point through the

stop bit. The processor must read the RDR before the next stop bit, or an overrun error occurs. Figure 7 shows the relationship between  $\overline{\mbox{IRQ}}$  and RxD for the continuous Data Receive mode.

Figure 7. Continuous Data Receive

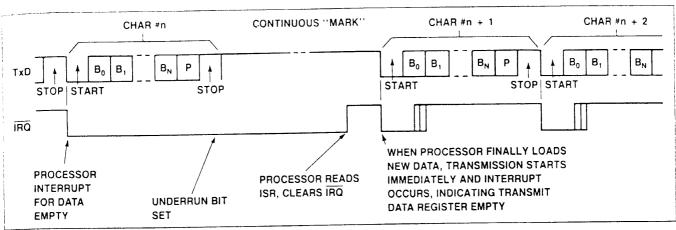

## TRANSMIT UNDERRUN CONDITION

If the MPU is unable to load the TDR before the last stop bit is sent, the TxD line goes to the MARK condition and the underrun

flag is set. This condition persists until the TDR is loaded with a new word. Figure 8 shows the relation between IRQ and TxD for the Transmit Underrun Condition.

Figure 8. Transmit Underrun Condition Relationship

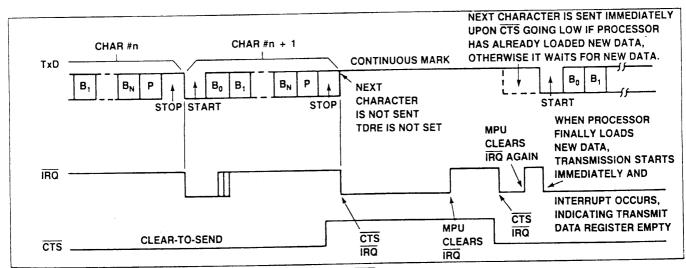

#### EFFECTS OF CTS ON TRANSMITTER

The CTS control line controls the transmission of data or the hand-shaking of data to a "busy" device (such as a printer). When the CTS line is low, the transmitter operates normally. Any transition on this line sets the CTS bit in the ISR. A high condition inhibits the TDRE bit in the ISR from becoming set. The word currently

in the shift register continues to be sent but any word in the TDR is held until  $\overline{\text{CTS}}$  goes low. At the high-to-low transition the  $\overline{\text{CTS}}$  bit in the ISR is again set. Figure 9 shows the relationship of  $\overline{\text{IRQ}}$ , TxD, and  $\overline{\text{CTS}}$  for the effects of  $\overline{\text{CTS}}$  on the transmitter.

Figure 9. Effects of CTS on Transmitter

#### R65C52

# Dual Asynchronous Communications Interface Adapter (DACIA)

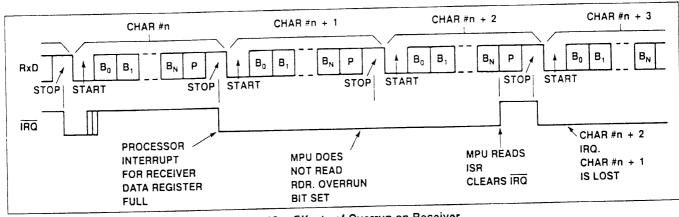

# EFFECTS OF OVERRUN ON RECEIVER

If the processor does not read the RDR before the stop bit of the next word, an overrun error occurs, the overrun bit is set in the ISR, and the new data word is not transferred to the RDR. The RDR contains the last word not read by the MPU and all follow-

ing data is lost. The receiver will return to normal operation when the RDR is read. Figure 10 shows the relation of  $\overline{\text{IRQ}}$  and RxD for the effects of overrun on the receiver.

Figure 10. Effects of Overrun on Receiver

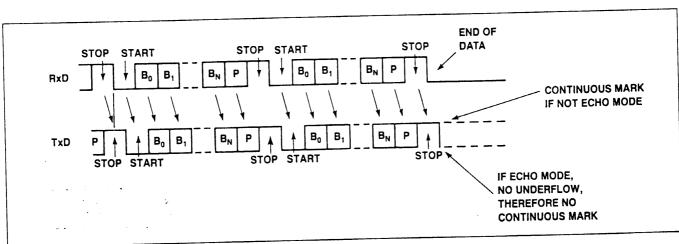

#### **ECHO MODE TIMING**

In the Echo Mode, the TxD line re-transmits the data received on the RxD line, delayed by 1/2 of a bit time. An internal underrun mode must occur before Echo Mode will start transmitting. In normal transmit mode if TDRE occurs (indicating end of data) an underflow flag would be set and continuous Mark transmitted. If Echo is initiated, the underflow flag will not be set at end of data and continuous Mark will not be transmitted. Figure 11 shows the relationship of RxD and TxD for Echo Mode.

Figure 11. Echo Mode Timing

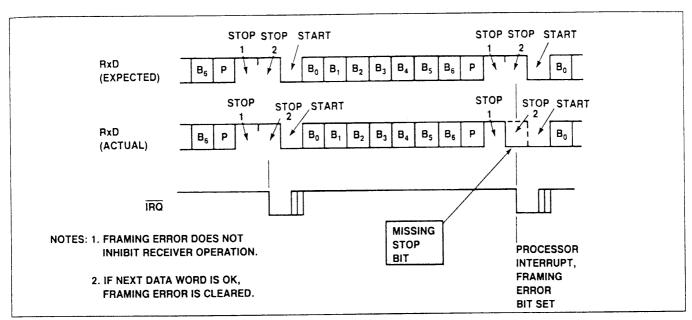

#### FRAMING ERROR

Framing error is caused by the absence of stop bit(s) on received data. The framing error bit is set when the RDRF bit is set. Subsequent data words are tested separately, so the status bit always

reflects the last data word received. Figure 12 shows the relationship of IRQ and RxD when a framing error occurs.

Figure 12. Framing Error

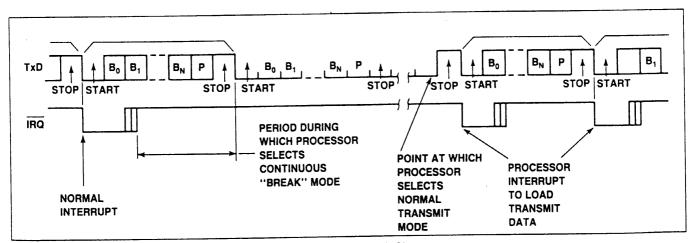

#### TRANSMIT BREAK CHARACTER

A Break may be transmitted by storing a value of \$00 in the IER. After storing zero in the IER the Break is transmitted immediately. Care should be exercised so that a character in transmission is not disturbed inadvertently. The Break level lasts until other than \$00 is stored in the IER at which time a stop bit is sent and

transmission may resume. At least one full word time of Break will be sent regardless of the length of time between starting and stopping the Break character. Figure 13 shows the relationship of IRQ and TxD for a Transmit Break character.

Figure 13. Transmit Break Character

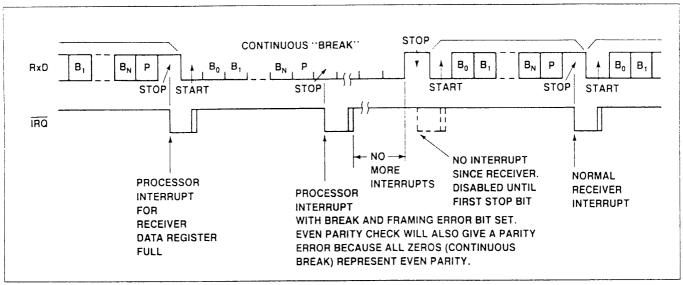

#### RECEIVE BREAK CHARACTER

In the event that a Break character is received by the receiver, the Break bit is set. The receiver does not set the RDRF bit and remains in this state until a stop bit is received. At this time the

next character is to be received normally. Figure 14 shows the relationship of  $\overline{IRQ}$  and RxD for a Receive Break Character.

Figure 14. Receive Break Character

#### **AUTOMATIC ADDRESS RECOGNITION**

The DACIA offers a unique solution to the standard problem associated with multi-drop environment UARTs and communication interface controllers. In the standard configuration used by other devices, the slave CPU must be constantly interrupted to analyze incoming characters on the communications net to determine if an address word is present and if so, does that address match the address assigned to the slave UART. This CPU interrupt scheme can become intolerable in very large multi-drop networks because every slave on the communications net must "wake-up" it's CPU for every character sent down the network by the master. The end result is that the CPUs on the communications net are constantly being interrupted for the mundane task of address recognition.

To avoid this constant CPU interrupt problem, the DACIA has been designed to do address comparison and recognition internally without the need for CPU intervention. Therefore, the slave CPU is not interrupted until the DACIA has determined that the character sent over the communications net by the master was an address and the address matched the address stored in the DACIA Compare Register. At this point the DACIA interrupts the CPU, goes out of Compare Mode, and receives the string of characters being transmitted by the master, (i.e., the data characters). When all data has been received by the slave, it's CPU must again write the slave address into the DACIA Compare Register which automatically puts it back into the Compare Mode, waiting for another address character.

# GENERATION OF NON-STANDARD BAUD RATES

#### **Divisors**

The internal counter/divider circuit selects the appropriate divisor for the crystal frequency by means of bits 0-3 of the CFR Control Register, as shown in Table 4.

#### **Generating Other Baud Rates**

By using a different crystal, other baud rates may be generated.

These can be determined by:

Furthermore, it is possible to drive the DACIA with an off-chip oscillator to achieve other baud rates. In this case, XTALI (pin 3) must be the clock input and XTALO (pin 4) must be a nonconnect.

Table 4. Divisor Selection

| Control<br>Register<br>Bits |               | Divisor Selected<br>For The | Baud Rate Generated<br>With 3.6864 MHz | Baud Rate Generated<br>With a Crystal<br>of Frequency (f) |                                              |                  |

|-----------------------------|---------------|-----------------------------|----------------------------------------|-----------------------------------------------------------|----------------------------------------------|------------------|

| 3                           | 2             | 1                           | 0                                      | Internal Counter                                          | Crystal                                      | f/73,728         |

| 0                           | 0             | 0                           | 0                                      | 73,728                                                    | $(3.6864 \times 10^6)/73,728 = 50$           |                  |

| 0                           | 0             | 0                           | 1                                      | 33,538                                                    | $(3.6864 \times 10^{\circ})/33,538 = 109.92$ | f/33,538         |

| 0                           | 0             | 1                           | 0                                      | 27,408                                                    | $(3.6864 \times 10^{6})/27,408 = 134.58$     | f/27,408         |

| 0                           | 0             | 1                           | 1                                      | 24,576                                                    | $(3.6864 \times 10^{\circ})/24,576 = 150$    | f/24,576         |

| 0                           | 1             | 0                           | 0                                      | 12,288                                                    | $(3.6864 \times 10^{\circ})/12,288 = 300$    | f/12,288         |

| 0                           | 1             |                             | 1                                      | 6,144                                                     | $(3.6864 \times 10^4)/6,144 = 600$           | f/6,144          |

| 0                           | 1             |                             | 0                                      | 3,072                                                     | $(3.6864 \times 10^{\circ})/3,072 = 1,200$   | f/3,072          |

| 0                           | 1             |                             | 1                                      | 2,048                                                     | $(3.6864 \times 10^{6})/2,048 = 1,800$       | f/2,048          |

| 1                           |               | <u>'</u>                    | 0                                      | 1,536                                                     | $(3.6864 \times 10^6)/1,536 = 2,400$         | f/1,536          |

| 1                           | <del></del> 0 | 0                           | 1                                      | 1,024                                                     | $(3.6864 \times 10^{6})/1,024 = 3,600$       | f/1,024          |

|                             |               | 1                           | <u>'</u>                               | 768                                                       | $(3.6864 \times 10^{4})/768 = 4,800$         | f/768            |

| 1                           | 0             | <u>'</u>                    |                                        | 512                                                       | $(3.6864 \times 10^6)/512 = 7,200$           | f/512            |

| 1                           | 1             | <u>'</u> _                  | <del></del>                            | 384                                                       | $(3.6864 \times 10^6)/384 = 9,600$           | f/384            |

| <u> </u>                    | 1             |                             | 1                                      | 192                                                       | $(3.6864 \times 10^6)/192 = 19,200$          | f/192            |

| 1                           | 1             | 1                           | 0                                      | 96                                                        | $(3.6864 \times 10^{\circ})/96 = 38,400$     | f/96             |

|                             |               |                             |                                        | 16                                                        | TxC/16 = Baud Rate or Rx                     | C/16 = Baud Rate |

Figure 15. DACIA External Clock Timing — Receive Data

Figure 16. DACIA External Clock Timing — Transmit Data

# AC CHARACTERISTICS

$(V_{CC} = 5.0V \pm 5\%, V_{SS} = 0V, T_A = T_L \text{ to } T_H)$

1. All times are in nanoseconds.

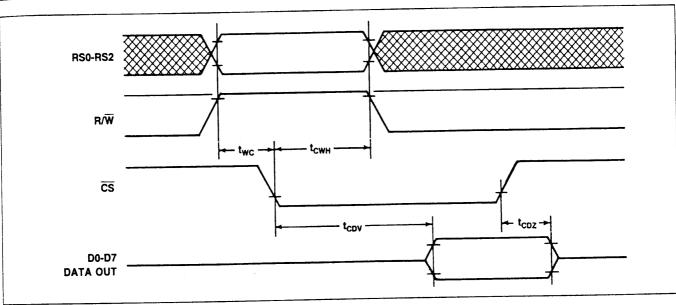

# READ/WRITE TIMING

|                                              |                  | 2 ! | ИНZ | 4 MHz |     |      |

|----------------------------------------------|------------------|-----|-----|-------|-----|------|

| Characteristic                               | Symbol           | Min | Max | Min   | Max | Unit |

| R/W, RS0-RS2 Valid to CS Low<br>(Setup Time) | twc              | 0   | _   | 0     |     | ns   |

| CS Low to R/W, RS0-RS2<br>(Hold Time)        | t <sub>CWH</sub> | 65  |     | 65    |     | ns   |

| CS Low to Data Valid                         | t <sub>CDV</sub> | _   | 100 | -     | 100 | ns   |

| CS High to Data Invalid<br>(Hold Time)       | tcoz             |     | 10  | _     | 10  | ns   |

| Data Valid to CS High                        | tovch            | 20  |     | 20    |     | ns   |

**DACIA Read Cycle Waveforms** RS0-RS2 R/W  $\overline{\text{cs}}$ D0-D7 DATA IN

**DACIA Write Cycle Waveforms**

# R65C52

# Dual Asynchronous Communications Interface Adapter (DACIA)

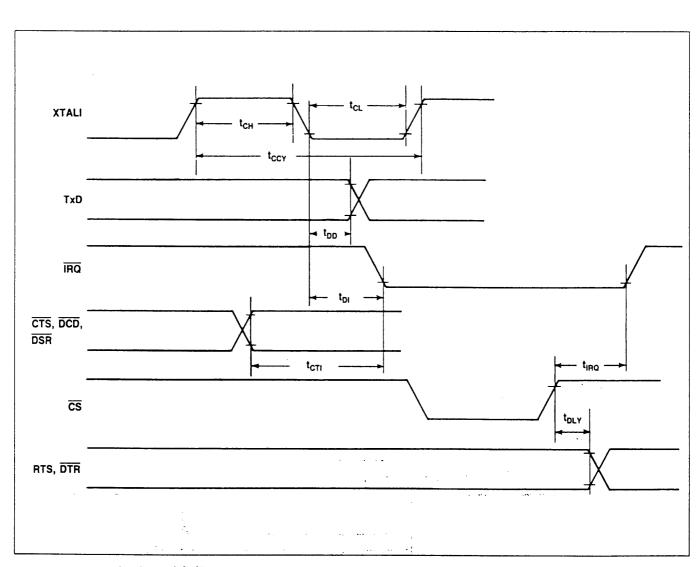

#### TRANSMIT/RECEIVE TIMING

| Characteristic                   | Symbol           | Min | Max | Unit |

|----------------------------------|------------------|-----|-----|------|

| Transmit/Receive Clock Rate      | tccy             | 250 | _   | ns   |

| Transmit/Receive Clock High Time | t <sub>CH</sub>  | 100 | _   | ns   |

| Transmit/Receive Clock Low Time  | t <sub>CL</sub>  | 100 | _   | ns   |

| XTALI to TxD Propagation Delay   | too              | _   | 250 | ns   |

| XTALI to IRQ Propagation Delay   | t <sub>DI</sub>  | _   | 250 | ns   |

| CTS, DCD, DSR to IRQ             | t <sub>CTI</sub> | _   | 150 | ns   |

| IRQ Propagation Delay (Clear)    | t <sub>IRQ</sub> | _   | 150 | ns   |

| RTS, DTR Propagation Delay       | toly             | _   | 150 | ns   |

**DACIA Transmit/Receive Timing**

# ABSOLUTE MAXIMUM RATINGS\*

| Parameter                                         | Symbol           | Value                    | Unit |

|---------------------------------------------------|------------------|--------------------------|------|

| Supply Voltage                                    | V <sub>CC</sub>  | -0.3 to $+7.0$           | Vdc  |

| Input Voltage                                     | V <sub>IN</sub>  | $-0.3$ to $V_{CC} + 0.3$ | Vdc  |

| Output Voltage                                    | V <sub>OUT</sub> | $-0.3$ to $V_{CC} + 0.3$ | Vdc  |

| Operating Temperature<br>Commercial<br>Industrial | T <sub>A</sub>   | 0 to +70<br>-40 to +85   | °C   |

| Storage Temperature                               | T <sub>STG</sub> | - 55 to + 150            | °C   |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **OPERATING CONDITIONS**

| Parameter                                     | Symbol          | Value                         |

|-----------------------------------------------|-----------------|-------------------------------|

| Supply Voltage                                | V <sub>CC</sub> | 5V ± 5%                       |

| Temperature Range<br>Commercial<br>Industrial | T <sub>A</sub>  | 0° to 70°C<br>- 40°C to +85°C |

### DC CHARACTERISTICS

( $V_{CC}$  = 5.0 V ±5%,  $V_{SS}$  = 0V,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted)

| Characteristic                                                                        | Symbol           | Min            | Тур | Max                                            | Unit     | Test Conditions                                                 |

|---------------------------------------------------------------------------------------|------------------|----------------|-----|------------------------------------------------|----------|-----------------------------------------------------------------|

| Input High Voltage Except XTALI and XTALO XTALI and XTALO                             | V <sub>IH</sub>  | + 2.0<br>+ 2.4 |     | V <sub>CC</sub> + 0.3<br>V <sub>CC</sub> + 0.3 | V        |                                                                 |

| Input Low Voltage Except XTALI and XTALO XTALI and XTALO                              | V <sub>IL</sub>  | - 0.3<br>- 0.3 |     | + 0.8<br>+ 0.4                                 | V        |                                                                 |

| Input Leakage Current<br>R/W, RES, RS0, RS1, RS2, RxD, CTS, DCD, DSR, RxC,<br>TxC, CS | I <sub>IN</sub>  |                | 10  | 50                                             | μА       | $V_{IN} = 0V \text{ to } V_{CC}$ $V_{CC} = 5.25V$               |

| Input Leakage Current for Three-State Off D0-D7                                       | I <sub>TSI</sub> |                | ±2  | 10                                             | μА       | $V_{IN} = 0.4V \text{ to } 2.4V$<br>$V_{CC} = 5.25V$            |

| Output High Voltage D0-D7, TxD, CLK OUT, RTS, DTR                                     | V <sub>OH</sub>  | + 2.4<br>1.5   | =   | _                                              | V        | $V_{CC} = 4.75V$ $I_{LOAD} = -100 \mu\text{A}$                  |

| Output Low Voltage D0-D7, TxD, CLK OUT, RTS, DTR                                      | V <sub>OL</sub>  |                | -   | +0.4                                           | ٧        | $V_{CC} = 4.75V$ $I_{LOAD} = 1.6 \text{ mA}$                    |

| Output Leakage Current (Off State)                                                    | l <sub>OFF</sub> | _              | ±2  | ±10                                            | μА       | $V_{CC} = 5.25V$ $V_{OUT} = 0 \text{ to } 2.4V$                 |

| Power Dissipation                                                                     | P <sub>D</sub>   | _              |     | 10                                             | mW/MHz   |                                                                 |

| Input Capacitance Except XTALI and XTALO XTALI and XTALO                              | C <sub>IN</sub>  | =              | _   | 5<br>10                                        | pF<br>pF | $V_{CC} = 5.0V$ $V_{IN} = 0V$ $f = 2 MHz$ $T_{A} = 25^{\circ}C$ |

| Output Capacitance                                                                    | C <sub>OUT</sub> | _              | -   | 10                                             | pF       | 1A - 23 0                                                       |

#### Notes:

- 1. All units are direct current (dc) except for capacitance.

- 2. Negative sign indicates outward current flow, positive indicates inward flow.

- 3. Typical values are shown for  $V_{\rm CC} = 5.0 \text{V}$  and  $T_{\rm A} = 25 ^{\circ} \text{C}$ .

#### PACKAGE DIMENSIONS